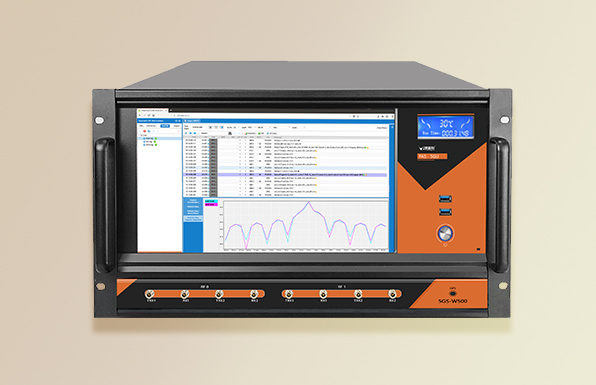

YunSDR Y780s是基于AMD Zynq UltraScale+ ZU19EG和ADI ADRV902x系列构建的高性能多通道软件无线电平台,频段范围75MHz到6GHz,支持八组发射和接收通道,瞬时带宽可达200MHz。数据传输接口采用2组100G光纤,通过PCIe3.0x16的可编程FPGA前传卡实现与上位机的实时交互。此外,设备提供了标准的控制和调试接口,包括USB-JTAG,10/100/1000M以太网,TF卡,USB3.0等。启动模式开关可以灵活配置各种启动方式,12V直流供电。

YunSDR Y780s

面向测向与通信融合的软件无线电

-

ꁸ 回到顶部

-

ꂅ 010-62670519

-

ꁗ QQ客服

-

ꀥ 微信专属客服

YunSDR 7系列型号对比

主要特点和接口

高通道密度和高集成度

75MHz to 6GHz频段范围 (可扩展至毫米波频段)

8路发射,8路接收

四核ARM Cortex-A53处理器,最高主频1.2 GHz

2个QSFP28光口(支持 40G/100G Aurora和自定义协议)

提供PCIe前传加速卡,PCIe Gen3 x 16接口, Xilinx Kintex-Ultrascale+ KU15P FPGA, 2个QSFP28光口

参考时钟输入输出

单机模式(嵌入式)或主机模式(100G转PCIe流模式)两种开发方式

瞬时带宽200MHz

Xilinx Zynq-Ultrascale+ ZU19EG Soc

IQ 采样时钟254.76MSPS

双核ARM Cortex-R5F 处理器,最高主频500MHz

QSFP+光口(支持1G/10G以太网)

千兆以太网RJ45

触发信号输入输出

内置GPSDO

USB3.0主机/设备接口

FPGA GPIO接口

Type C USB串口控制台和JTAG

Y750Neo

大带宽

1MHz~8GHz

Y750s

大带宽

1MHz~6GHz

Y780s

75MHz~6GHz

ADRV9026+ZU19EG

FX200(100G)

4 ADCs & 4 DACs

订货型号

产品定位

ADC最高采样率

频段范围

多通道,多资源

Y790s

多通道,大带宽

1MHz~6GHz

核心器件

RFSoC

RFSoC

RFSoC

标配加速卡

FX200(100G)

FX200(100G)

FX200(100G)

选配加速卡

FX800

FX800

FX800

FX800

通道数量

4 ADCs & 4 DACs

8路Transceiver

8 ADCs & 8 DACs

5Gsps

5Gsps

245.76Msps

5Gsps

IQ采样率

1000MHz 983.04MHz 960MHz

1000MHz 983.04MHz 960MHz

245.76MHz

1000MHz 983.04MHz 960MHz

40G前传能力(标配)

1000MHz 1通道 500MHz 2通道 250MHz 4通道

1000MHz 1通道 500MHz 2通道 250MHz 4通道

245.76MHz 4通道 122.88MHz 8通道

1000MHz 1通道 500MHz 2通道 250MHz 4通道 125MHz 8通道

100G前传能力(选配)

1000MHz 2通道 500MHz 4通道

1000MHz 2通道 500MHz 4通道

245.76MHz 8通道

1000MHz 2通道 500MHz 4通道 250MHz 8通道

可编程逻辑资源(LCs)

930K

930K

1143K

930K

可编程DSP单元数量(DSP Slices)

4272个

4272个

1968个

4272个

PS:64位,4GB;

PL:32位,2GB

DDR4资源

PS:64位,4GB;

PL:32位,2GB

PS:64位,4GB;PL:64位双通道,4GB x2 ,共8GB

PS:64位,4GB;PL:64位双通道,4GB x2 ,共8GB

高速数据接口

1x 100G QSFP28, 兼容40G模式 1x 10G SFP+,兼容1G以太网

2x 100G QSFP28,兼容40G模式 1x 10G SFP+,兼容1G以太网

2x 100G QSFP28,兼容40G模式 1x 10G SFP+,兼容1G以太网

1x 100G QSFP28, 兼容40G模式 1x 10G SFP+,兼容1G以太网

其他接口

编程接口

USB3.0

USB-JTAG

USB3.0

USB3.0

USB3.0

USB-JTAG

USB-JTAG

USB-JTAG

产品描述

YunSDR Y780s是基于AMD Zynq UltraScale+ ZU19EG和ADI ADRV902x系列构建的高性能多通道软件无线电平台,频段范围75MHz到6GHz,支持八组发射和接收通道,瞬时带宽可达200MHz。数据传输接口采用2组100G光纤,通过PCIe3.0x16的可编程FPGA前传卡实现与上位机的实时交互。此外,设备提供了标准的控制和调试接口,包括USB-JTAG,10/100/1000M以太网,TF卡,USB3.0等。启动模式开关可以灵活配置各种启动方式,12V直流供电。

YunSDR Y780s将八个发射通道和八个接收通道整合到一个体积紧凑的小型机箱,使其更容易运输以适应外场测试和操作。通道还可以通过内部恒温晶体振荡器 (OCXO) 同步,内部 GPS 驯服振荡器 (GPSDO)用于时间戳 ,可提供10 MHz参考和每秒脉冲 (PPS) 。

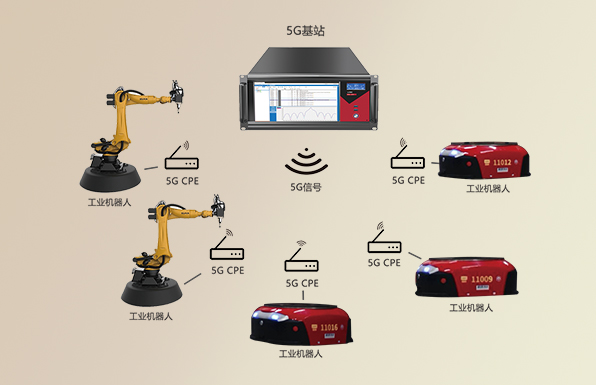

开箱即用的软件工具可以实现设备自检,频谱分析,记录回放等无线信号处理常用功能, 帮助工程师快速定位和解决无线领域相关问题。设备驱动支持GNU Radio等主流的开源项目,也支持FPGA底层开发,用户可以快速的进行原型机验证和可靠地部署各种SDR应用,如5G基站、信号情报和频谱监测等。

全频谱全带宽

产品功能

未来的无线系统需要更强大的计算能力来处理日益复杂的算法,这个时候单一板卡往往不能满足要求,需要将数据传递给更加强大的计算系统,比如FPGA阵列或者计算机集群。高速光纤接口成了高性能SDR系统的标配,光口的数量和速率是数据传输带宽的关键。

YunSDR Y780s采用了双100G光口作为系统对外的数据通道,通过FPGA前传加速卡,将100G光口转换成了PCIe3.0接口,并且提供了完善驱动和API接口库,用户可以直接调用接口函数来获取数据,可以支持100G接口的满速率通信。另外,FPGA加速卡的FPGA采用开放接口,支持用户自己二次开发,实现算法的加速。

更快接口

系统标配的FX200加速卡采用了Xilinx Kintex UltraScale+系列FPGA KU15P作为加速芯片,16nm工艺的FPGA提供了丰富的信号处理资源。如果需要更大规模的FPGA处理能力,可以选择升级到FX800加速卡。 FX800采用了Xilinx Virtex UltraScale+系列 FPGA VU13P作为加速芯片,提供了更加丰富的信号处理资源。

软件定义无线电平台

联系我们

咨询热线

010-6267 0519

5G/6G原型验证与测试

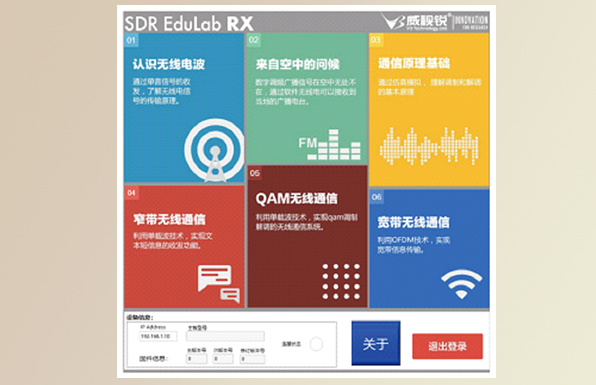

工程教育与实验室建设

关于威视锐